Overview

if opcode == Add {

// do addition

}

if opcode == SRead {

// do storage read

}

...if opcode == Add {

// do addition

}

if opcode == SRead {

storage_queue.push((address, value));

// proof storage read in other circuit

}

...Public Input Structure

start flag

Boolean that shows if this is the first instance of corresponding circuit type

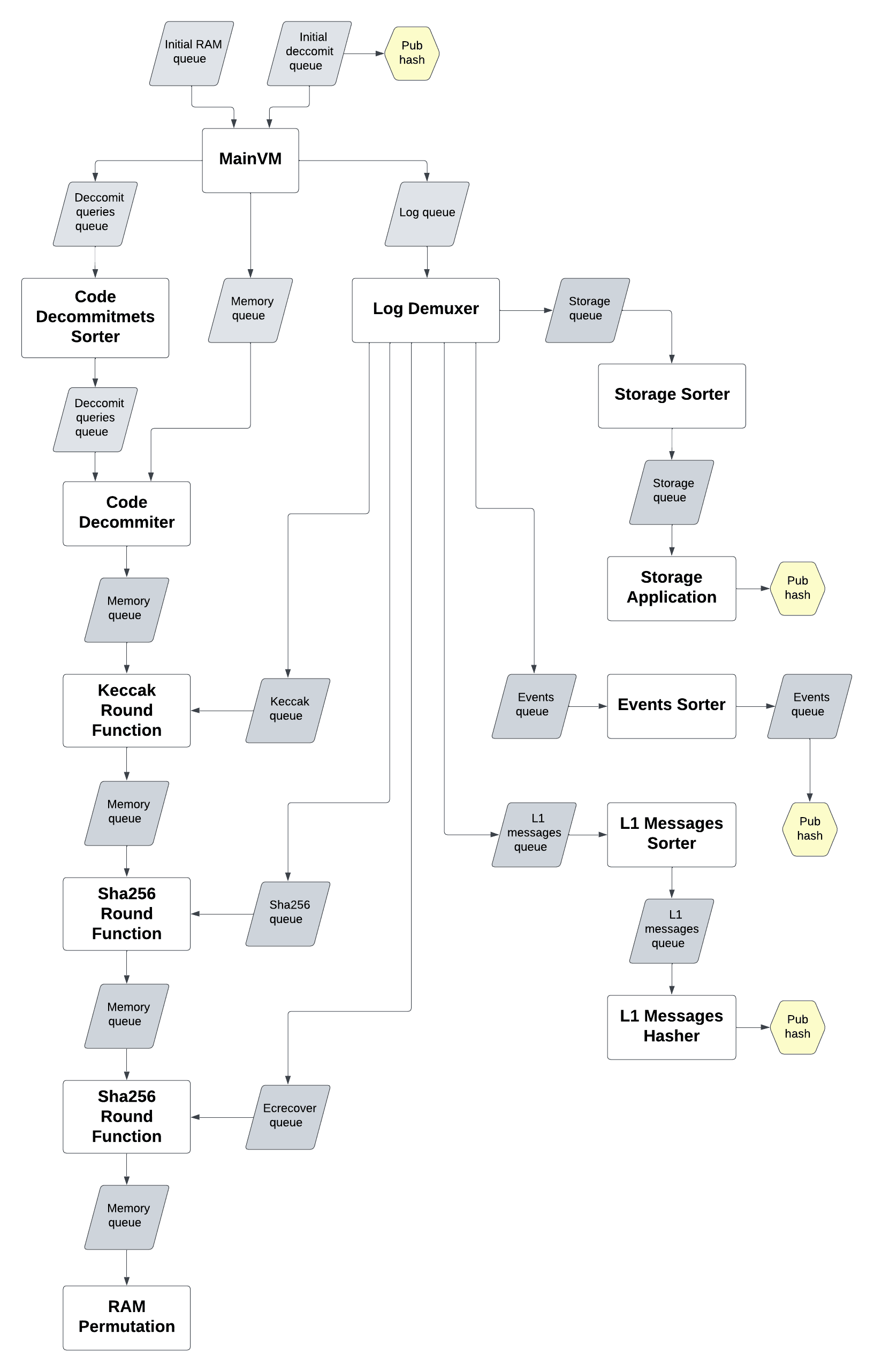

Overall View of Base Layer Circuits

Base Layer Circuits

Last updated